Chip Scale Power and Energy

University

Course

VVG

Sponsor

NASA-JPL; Duracell; SOCOM

Goals

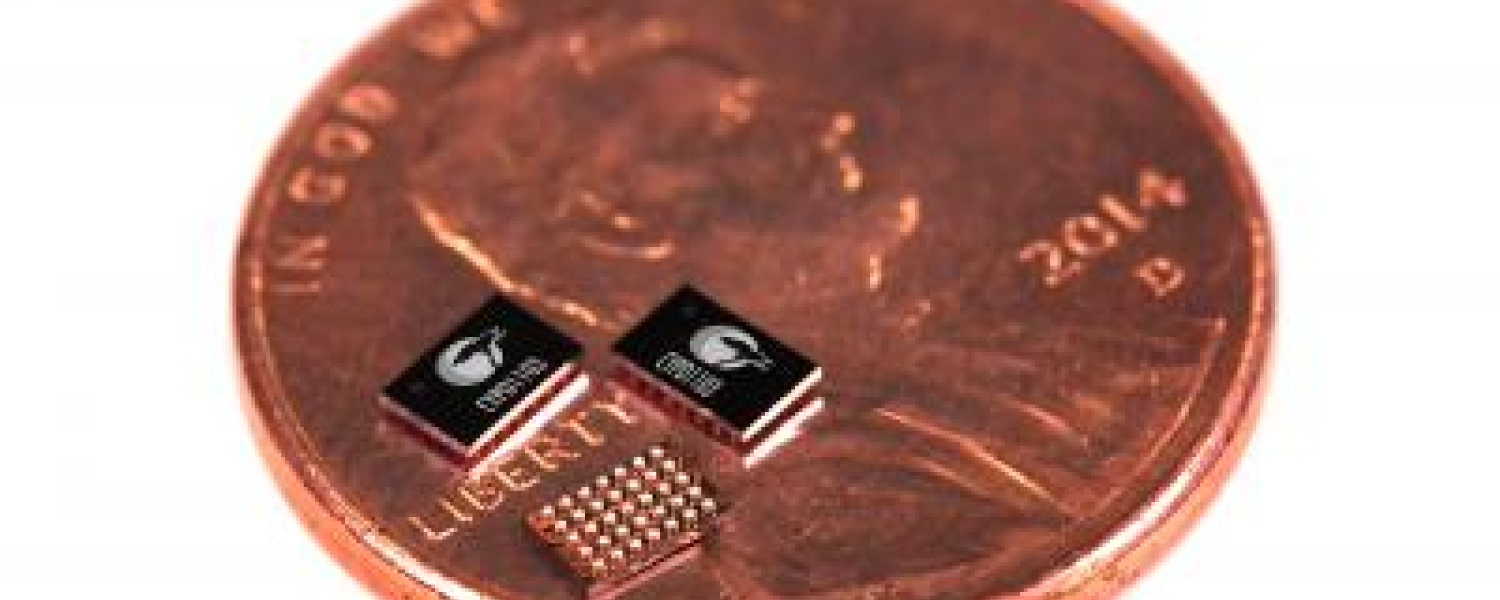

Due to ITAR and other access restrictions this project is limited to US citizens only. To develop nanostructured chip-scale power and energy storage devices for use in miniaturized sensing, communication and energy harvesting devices.

Issues

This vertically integrated project (VIP) will create and characterize in operando chip-scale electrochemical double layer (ECDL) supercapacitors that feature a functionalized pseudocapacitive architecture coupled with a tailored ionic-liquid-based electrolyte for rechargeable energy storage. Future years will integrate these devices into miniature sensors, energy harvesters, and IoT communication devices. Student researchers will fabricate supercapacitor electrodes using carbon nanotubes (CNTs) embedded within a silicon wafer. The CNTs will be further functionalized by both chemical and physical techniques, such as atomic layer deposition. The functionalized pseudocapacitive architecture will then be coupled with a tailored ionic-liquid-based electrolyte. The chip-scale devices will be packaged hermetically for incorporation as viable prototypes on mission architectures.

Tools and Methods

Cleanroom Microfabrication

Nanomaterial Synthesis

Electron Microscopy

In Situ Raman Spectroscopy

Electrical Design

Desired Majors

Materials Science and Engineering

Electrical Engineering

Computer Engineering

Mechanical Engineering

Sponsor

NASA-JPL; Duracell; SOCOM